日本NCT器件研究新突破!横向结型场效应晶体管(JFET)突破10kV击穿极限

来自美国和日本的研究团队报告了一种击穿电压超过 10 kV 增强型(E-mode)氧化镓(Ga2O3)横向结型场效应晶体管(JFETs),该器件采用了氧化镍(NiO)降低表面电场(RESURF)结构和混合漏极(hybrid-drain)的设计,工作温度可达250°C [Yuan Qin et al, IEDM, session 25-5, 2024]。

该团队由美国弗吉尼亚理工大学、美国海军研究实验室和日本 Novel Crystal Technology 组成,其研究成果于 2024 年 12 月 IEEE 国际电子器件会议(IEDM 2024)上发布。研究人员表示:"我们的器件展示了最高的平均电场强度,并首次报告了碳化硅(SiC)以外的高压晶体管在 250°C 下的工作温度和 3 kV 的可靠性数据。"

Ga2O3 具有 4.8 eV 的超宽禁带(UWBG),而氮化镓(GaN)和碳化硅(SiC)的禁带宽度分别为 3.4 eV 和 3.3 eV。10 kV 的击穿性能使这些 JFETs 进入中压(1-35kV)功率电子器件领域,有望在电网和可再生能源设施中得到广泛应用。

研究人员指出:"高压(HV)器件的出现可显著减少器件数量、简化电路拓扑,改善系统尺寸,提高可靠性。目前商用高压器件以 6.5 kV 的硅 IGBT 为主;SiC MOSFET 的工程样品可达 10 kV。"

与其他宽禁带半导体材料不同,Ga2O3 可制备出直径达 6 英寸的衬底晶圆,其晶体材料可通过熔融法生长。增强型(常关型,即在零栅压下阻断电流)晶体管通常因其功耗更低且具有故障安全特性,而更受功率电子领域青睐。

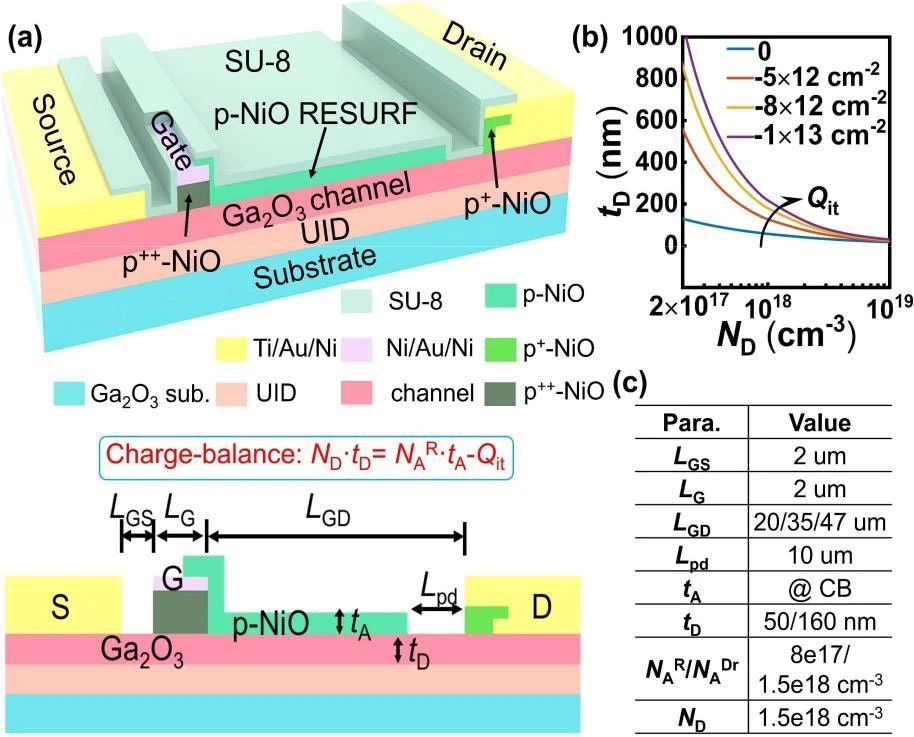

器件设计(图1)主要针对 E-mode 操作、电荷平衡和导通电阻(Ron)进行优化。器件包含 n 型 Ga2O3 沟道、混合 p-NiO/金属漏极、重掺杂 p 型 NiO 栅极以及 p-NiO RESURF 结构。

图1:(a) 采用 p-NiO RESURF 和混合漏极设计的 Ga2O3 JFET 示意图:三维结构图(上)与截面图(下)。(b) 为实现 E-mode 操作,计算的最大沟道厚度(tD)与施主掺杂浓度(ND)的关系曲线,界面电荷密度(Qit)范围为 013/cm2 至−1013/cm2。(c) 关键器件参数及数值表

NiO 区域在栅极 RESURF(R)和混合漏极(Dr)侧分离,以避免穿通。间隙两侧的 p 型掺杂浓度(NAR/NADr)可独立优化。RESURF 结构设计与英飞凌商用 GaN 栅极注入晶体管(GITs)类似。

外延材料通过分子束外延(MBE)在半绝缘(010)Ga2O3 衬底上生长,n 型沟道位于非故意掺杂(UID)层上。制备了两个样品 #A 和 #B,其 n 型沟道层厚度(td)分别为 50 nm 和 160 nm。更厚的沟道有助于降低 Ron。

器件制造始于硅注入与激活,随后沉积源/漏金属。通过氮离子注入实现电隔离。NiO 材料采用溅射沉积,通过调节氧分压依次形成混合漏极、p++ 型栅极和 RESURF 区域的不同受主浓度。栅极掺杂浓度超过 1019/cm3。

#A 和 #B 的阈值电压(VTH)分别达到 1.9 V 和 1.5 V,实现了 E-mode 操作。栅极电位因栅漏电流限制在 3.5-4V 范围。对应的比导通电阻(Ron,sp)分别为 703 mΩ·cm2 和 92 mΩ·cm2。

研究人员指出:"尽管 #A 器件的 td 薄 3.2 倍,但其 Ron 高 7 倍,表明栅极沟道对 Ron 的显著贡献——#A 器件栅下未耗尽 Ga2O3 导电沟道更窄。" 当器件温度升至 250°C 时,#A 器件的 VTH 降至 0.7 V,Ron 较 25°C 时增加 1.6 倍。团队写道:"Ron 的温度系数小于 10kV SiC MOSFET 的报道值,表明高温下传导损耗更低。”#B JFET 的 VTH 在约 100°C 时变为负值,150°C 时降至 -3.3 V。超过 175°C 后,栅极失去有效控制能力。

当栅极电位为 0 V 时,两个样品的击穿电压(BV)均超过 10 kV。通过调节器件参数至近电荷平衡状态实现最大 BV。最大 BV 对应的栅漏间距(LGD)为 47 μm。团队报告:"BV 时的平均横向电场为 1.75-2.45 MV/cm。" #A 器件在 250°C 高温下仍保持高 BV,而 #B 材料在高温下性能下降,150°C 时 BV 在 -10 V 栅压下低于 10 kV。

研究人员还进行了 150°C 高温栅偏压/反向偏压(HTGB/HTRB)可靠性测试。在 HTGB 测试中,#A 和 #B 器件的阈值电压偏移和导通电阻偏移分别在 0.32 V 和 35% 范围内,且完全可恢复。#B 器件的 HTRB 研究显示存在漏致势垒降低(DIBL)效应,VTH 偏移 -3 V(基本可恢复)。

研究人员解释:"#B 器件的厚沟道导致势垒降低和高压 VD 下的穿通。这种 DIBL 可能因 Qit 及其高温加速去俘获而恶化。" #A 器件的阈值偏移在 0.2 V 内,导通电阻增加了 34%,所有参数偏移均可完全恢复,但 #A 器件的缺点是由于沟道较窄导致导通电阻较高。

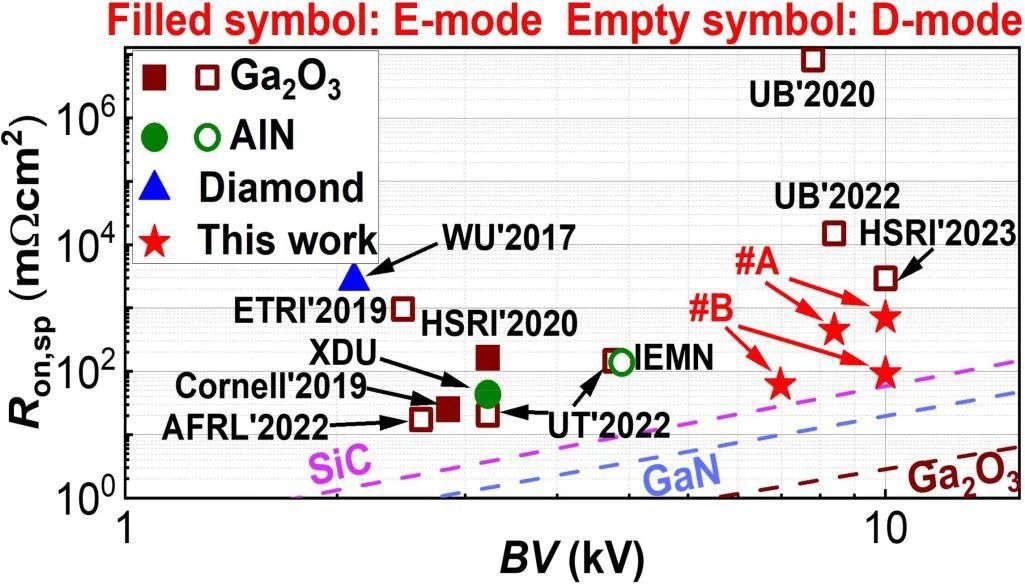

图2:比导通电阻(Ron,sp)与击穿电压(BV)的基准对比,针对击穿电压>2 kV 的超宽禁带(UWBG)功率晶体管。彩色虚线表示不同半导体材料(SiC/GaN/Ga2O3)的理论极限

通过对比文献中的 Ron,sp 和 BV 性能(图2),研究人员报告 #A 和 #B 器件的品质因数(FOMs,BV2/Ron,sp)分别至少为 142 MW/cm2 和 1086 MW/cm2(BV>10kV)。这些数值被宣称是"所有 BV > 3kV 的 UWBG 晶体管中的新纪录"。团队补充:"#A 器件也是所有 > 3 kV UWBG 晶体管中首个报道的 E-mode 器件。

文章链接:

https://www.semiconductor-today.com/news_items/2025/feb/virginia-130225.shtml

本文转载自《亚洲氧化镓联盟》订阅号